[ad_1]

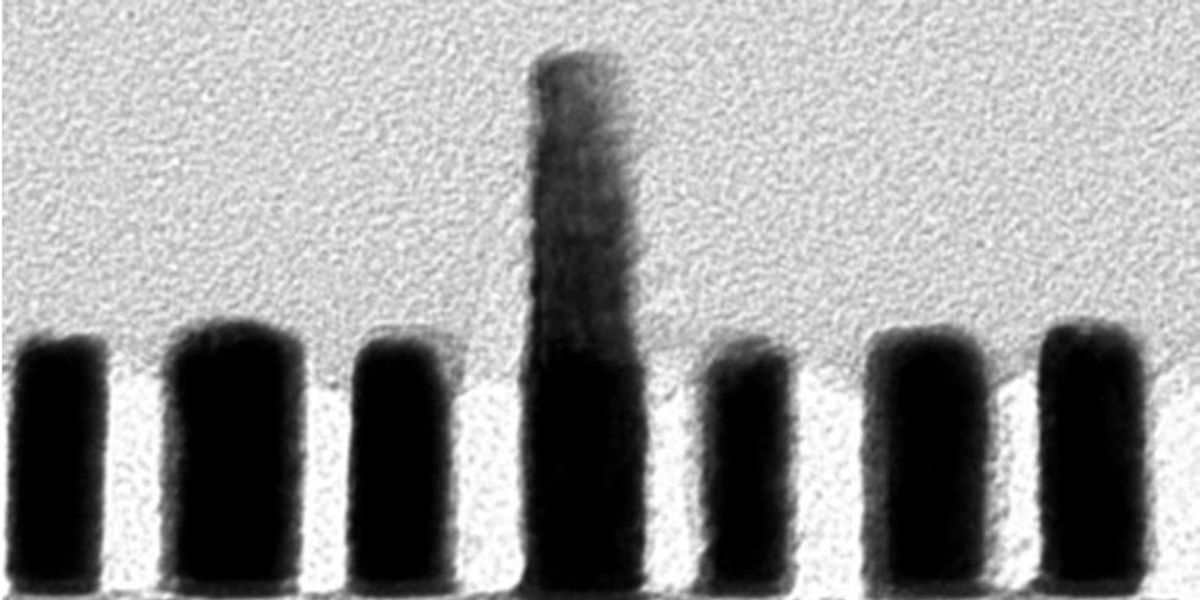

Interconnects—these generally nanometers-wide metallic wires that hyperlink transistors into circuits on an IC—are in want of a serious overhaul. And as chip fabs march towards the outer reaches of Moore’s Regulation, interconnects are additionally turning into the business’s choke level.“For some 20-25 years now, copper has been the metallic of selection for interconnects. Nevertheless we’re reaching a degree the place the scaling of copper is slowing down,” IBM’s Chris Penny, informed engineers final month on the IEEE Worldwide Electron Gadget Assembly (IEDM). “And there is a chance for various conductors.”Ruthenium is a number one candidate, but it surely’s not so simple as swapping one metallic for an additional, in response to analysis reported at IEDM 2022. The processes of how they’re shaped on a chip should be turned the other way up. These new interconnects will want a unique form and a better density. These new interconnects may even want higher insulation, lest signal-sapping capacitance take away all their benefit.Even the place the interconnects go is ready to vary, and shortly. However research are beginning to present, the good points from that shift include a sure value.Ruthenium, high vias, and air gapsAmong the replacements for copper, ruthenium has gained a following. However analysis is exhibiting that the previous formulation used to construct copper interconnects are a drawback to ruthenium. Copper interconnects are constructed utilizing what’s referred to as a damascene course of. First chip makers use lithography to carve the form of the interconnect into the dielectric insulation above the transistors. Then they deposit a liner and a barrier materials, which prevents copper atoms from drifting out into the remainder of the chip to muck issues up. Copper then fills the ditch. The truth is, it overfills it, so the surplus should be polished away.All that additional stuff, the liner and barrier, take up house, as a lot as 40-50 % of the interconnect quantity, Penny informed engineers at IEDM. So the conductive a part of the interconnects are narrowing, particularly within the ultrafine vertical connections between layers of interconnects, rising resistance. However IBM and Samsung researchers have discovered a method to construct tightly-spaced, low-resistance ruthenium interconnects that don’t want a liner or a seed. The method is named spacer assisted litho-etch litho-etch, or SALELE, and, because the identify implies, it depends on a double serving to of extreme-ultraviolet lithography. As an alternative of filling in trenches, it etches the ruthenium interconnects out of a layer or metallic after which fills within the gaps with dielectric.The researchers obtain the perfect resistance utilizing tall, skinny horizontal interconnects. Nevertheless, that will increase capacitance, buying and selling away the profit. Thankfully, as a result of method SALELE builds vertical connections referred to as vias—on high of horizontal interconnects as an alternative of beneath them—the areas between slender ruthenium strains can simply be crammed with air, which is the perfect insulator accessible. For these tall, slim interconnects “the potential good thing about including an air hole is big… as a lot as a 30 % line capacitance discount,” mentioned Penny.The SALELE course of “offers a roadmap to 1-nanometer processes and past,” he mentioned.Buried rails, back-side energy supply, and sizzling 3D chipsAs early as 2024, Intel plans to make a radical change to the placement of interconnects that carry energy to transistors on a chip. The scheme, referred to as back-side energy supply, takes the community of energy supply interconnects and strikes it beneath the silicon, so that they method the transistors from under. This has two foremost benefits: It permits electrical energy to stream by wider, much less resistive interconnects, resulting in much less energy loss. And it frees up room above the transistors for signal-carrying interconnects, which means logic cells might be smaller. (Researchers from Arm and the Belgian nanotech analysis hub Imec defined all of it right here.)At IEDM 2022, Imec researchers got here up with some formulation to make back-side energy work higher, by discovering methods to maneuver the tip factors of the ability supply community, referred to as buried energy rails, nearer to transistors with out messing up these transistors’ digital properties. However additionally they uncovered a considerably troubling drawback, back-side energy might result in a build-up of warmth when utilized in 3D stacked chips.First the excellent news: When imec researchers explored how a lot horizontal distance you want between a buried energy rail and a transistor, the reply was just about zero. It took some additional cycles of processing to make sure that the transistors have been unaffected, however they confirmed which you can construct the rail proper beside the transistor channel area—although nonetheless tens of nanometers under it. And that might imply even smaller logic cells.Now the unhealthy information: In separate analysis, imec engineers simulated a number of variations of the identical future CPU. Some had the type of energy supply community in use in the present day, referred to as front-side energy supply, the place all interconnects, each information and energy, are in-built layers above the silicon. Some had back-side energy supply networks . And one was a 3D stack of two CPUs, the underside having back-side energy and the highest having front-side.Again-side energy’s benefits have been confirmed by the simulations of the 2D CPUs. In comparison with front-side supply, it reduce the loss from energy supply in half, for instance. And transient voltage drops have been much less pronounced. What’s extra, the CPU space was 8 % smaller. Nevertheless, the most well liked a part of back-side chip was about 45 % hotter than the most well liked a part of a front-side chip. The doubtless trigger is that back-side energy requires thinning the chip right down to the purpose the place it must be bonded to a separate piece of silicon simply to stay secure. That bond acts as a barrier to the stream of warmth.Researchers examined a situation the place a CPU [bottom grey] with a back-side energy supply community is bonded to a second CPU having a front-side energy supply community [top grey].The actual issues arose with the 3D IC. The highest CPU has to get its energy from the underside CPU, however the lengthy journey to the highest had penalties. Whereas the underside CPU nonetheless had higher voltage-drop traits than a front-side chip, the highest CPU carried out a lot worse in that respect. And the 3D IC’s energy community ate up greater than twice the ability {that a} single front-side chip’s community would devour. Worse nonetheless, warmth couldn’t escape the 3D stack very effectively, with the most well liked a part of the underside die nearly 2.5 instances as sizzling as a single front-side CPU. The highest CPU was cooler, however not by a lot.The 3D IC simulation is admittedly considerably unrealistic, imec’s Rongmei Chen informed engineers at IEDM. Stacking two in any other case an identical CPUs atop one another is an unlikely situation. (It’s rather more widespread to stack reminiscence with a CPU.) “It’s not a very reasonable comparability,” he mentioned. But it surely does level out some potential points.From Your Website ArticlesRelated Articles Across the Internet

[ad_2]

Sign in

Welcome! Log into your account

Forgot your password? Get help

Privacy Policy

Password recovery

Recover your password

A password will be e-mailed to you.